CS111 Lecture Note 11/8

The purpose of the projects for this class is that it is important to learn how to deal with large amounts of code that you did not write yourself.

Midterm Problem 6

11 for (I = 0; I < MAXTHREADS; i++)

12 if (r->waiting[i] == 1) {

13 result = r->data[i];

14 r->data =[i] = data;

15 r->waiting[i] = 2;

16 return result;

}

19 r-> data[my_id] = data;

20 r->waiting[my_id] = 1;

21 while(r->waiting[my_id] != 2)

22 /* */;

no one is waiting

Thread 1 -> 19 -> waiting[i] =1

Thread 2 -> 19 -> waiting[i] = 1

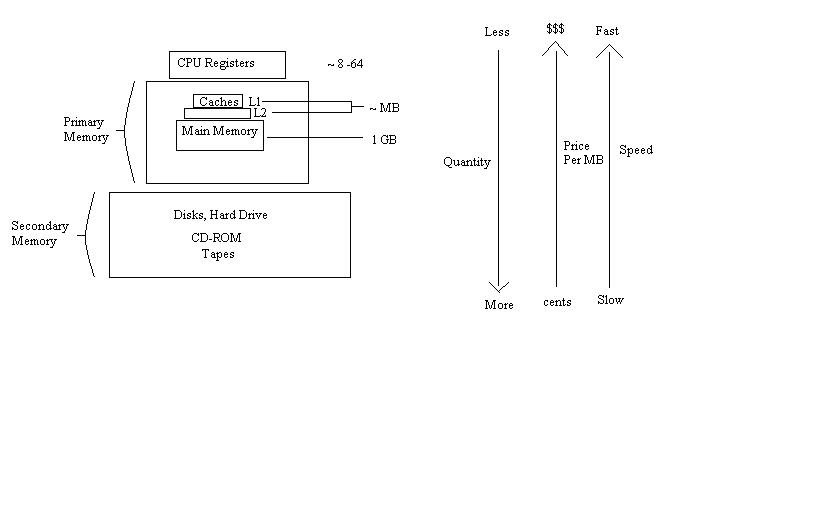

Managing Storage

- Memory

- Disks

- Other I/O devices that move data

- I/O methodologies

- Memory

- Virtual Memory

Scenario from last lecture:

Device Reads 40 byte “packets” from device

à disk = sectors

|

|

Overhead (how much CPU busy time) |

Latency (Wall clock time?) |

|

Cycle |

10-9 s |

|

|

Programmed I/O |

10-6 s (1000 cycles) |

|

|

Interrupt |

5 * 10-6 s (5000 cycles) |

|

|

Clock Interrupt |

5 * 10-6 s |

10-3 s |

|

Device Response |

|

50 * 10-6 s |

Read 1 packet from device using busy waiting

- Write command to device (5 PIO)

- Wait (50 PIO)

- While (device not ready) { /* */;}

- Read (1 PIO/Byte) = (40 PIO)

|

|

Overhead |

Latency |

Throughput |

|

|

CPU Busy |

Turn Around Time |

# Packets/Sec |

|

Polling w/Busy Wait |

95 μs |

95 μs |

10,000 p/s |

|

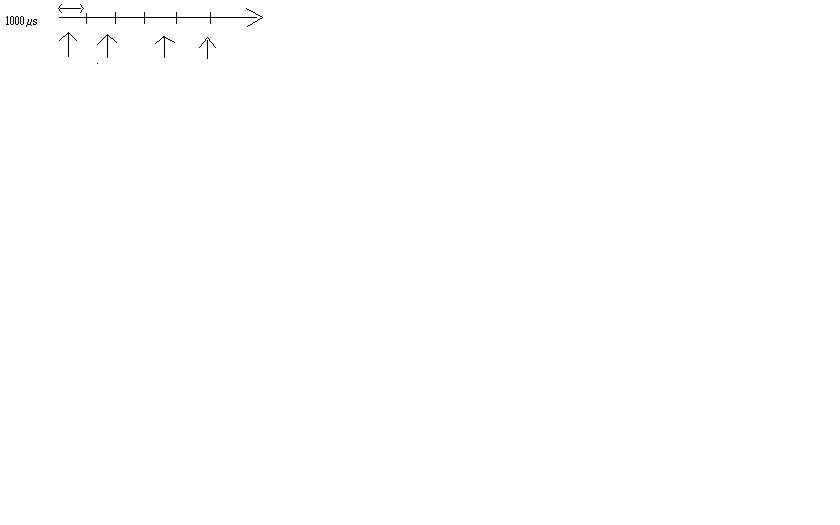

Clock Interrupt Polling |

46 μs |

~500 μs |

1000 p/s |

|

CLK INTR w/ Card Buff |

46 μs |

~500 μs |

21,700 p/s |

|

Card Interrupts (intr-driven) |

51 μs |

101 μs |

~19,000 p/s |

|

Interrupts w/DMA |

11 μs |

61 μs |

~90,900 p/s |

|

DMA w/Polling |

1 μs |

~51 μs |

1 million p/s |

*The highlighted numbers are the ones that affect the throughput

Clock Interrupt

- Write Command

- At every clock interrupt, check device ready

- Read Packet when device ready

- Write Command (5 PIO)

- Check Ready (1 PIO)

- Read (40 PIO)

Clock Interrupts w/Buffering

- Write a request before previous request completes

- Write command

- Clock interrupt, loop

While (a request ready)

Read that request

- This changes throughput to be based on overhead instead of latency

Device interrupts when done

- Write Command

- One device interrupt, check ready

- Read result

- Write Command (5 PIO)

- Interrupt (5 PIO)

- Check Ready (1 PIO)

- Read Data (40 PIO)

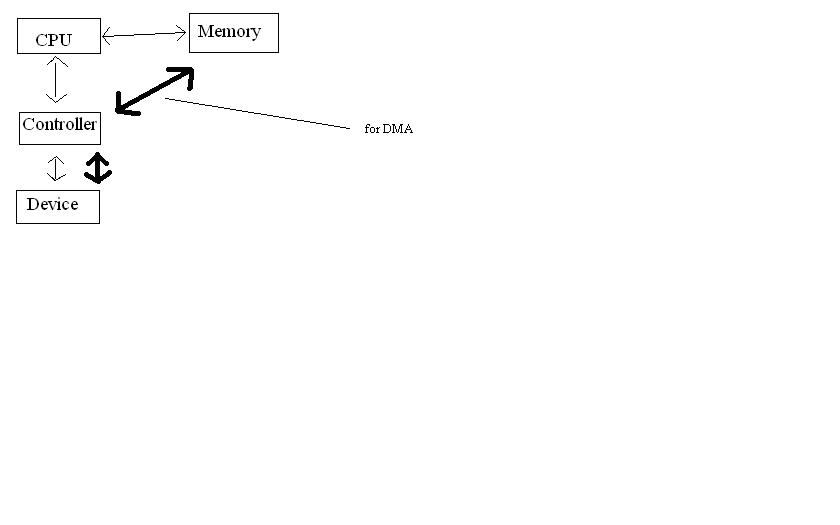

DMA:

Direct Memory Access

DMA & Interrupts

- Allocate packet space

- Write command, tell device to store data in packet space address

- Wait interrupt à check ready

CPU Overhead

- Write Command (5 PIO)

- Interrupt (5 PIO)

- Check Ready (1 PIO)

DMA w/ Polling

à Share command in a lock-free queue!

-Bottleneck shifts to bus

-Device does not interrupt the kernel for packets

Kernel

Write command

Writes command into memory at tail of queue, move tail ptr

Device

If head != tail

Read new command off ring

Execute command

Mark done, change ring

*Bottleneck shifts to the other item

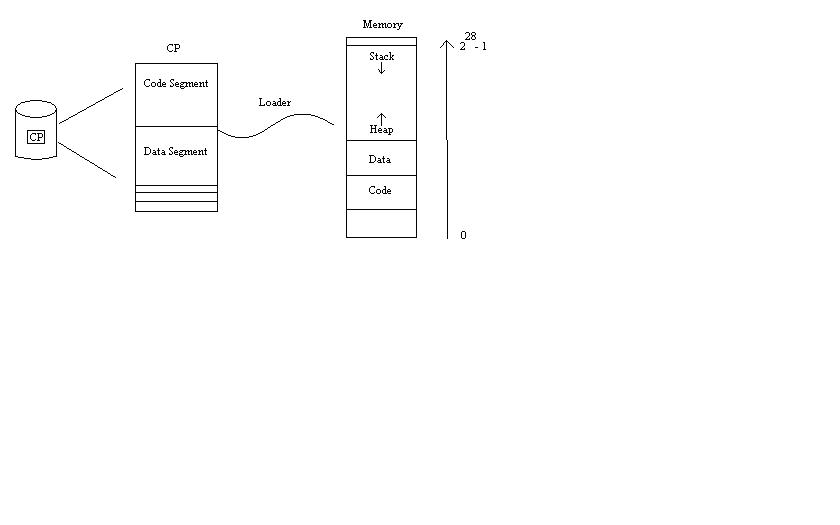

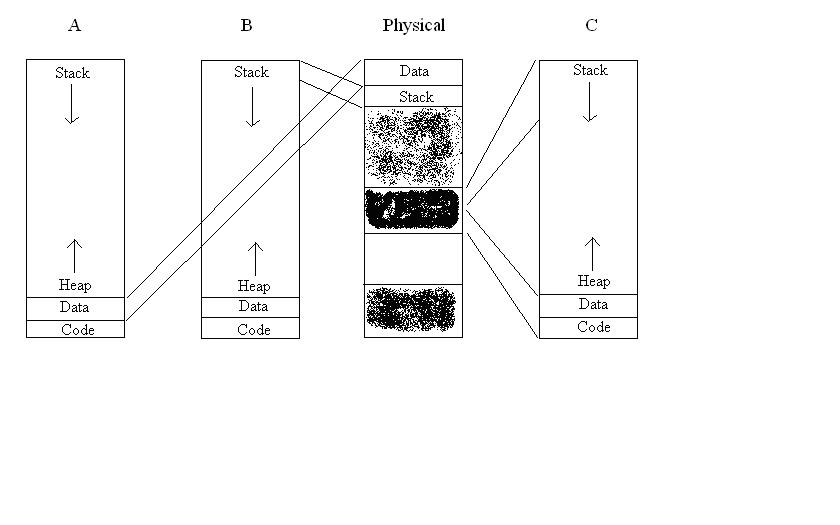

Managing Memory

What goes into a process’s memory space?

- Stacks

- Instructions à Code (in program)

- Global variables (data) (in program)

- Heap (dynamically allocated memory)

“segments” à a region of memory accessed for a single purpose à placed into a shared address space for the process

Multi-Process Address Space

- Run Processes A & B

- Loader

- Must rewrite addresses appropriately for load addresses (Dynamic Linking)

Problems

- Running out of address space before we run out of memory

- No memory isolation

How much space to leave for a heap?

- A lot of space à don’t run out artificially

- Internal fragmentation

- Memory unused inside an allocated block that cannot be reused

Virtual Memory

- Separates address space from memory storage

- Each process has its own independent address space

- Memory storage is accessed through indirection

NO Virtual Memory

Virtual Memory

Processor has a function that maps addresses to physical memory

à To allocate memory in a heap

à allocate physical memory from anywhere

à map it to A’s address space at the right location